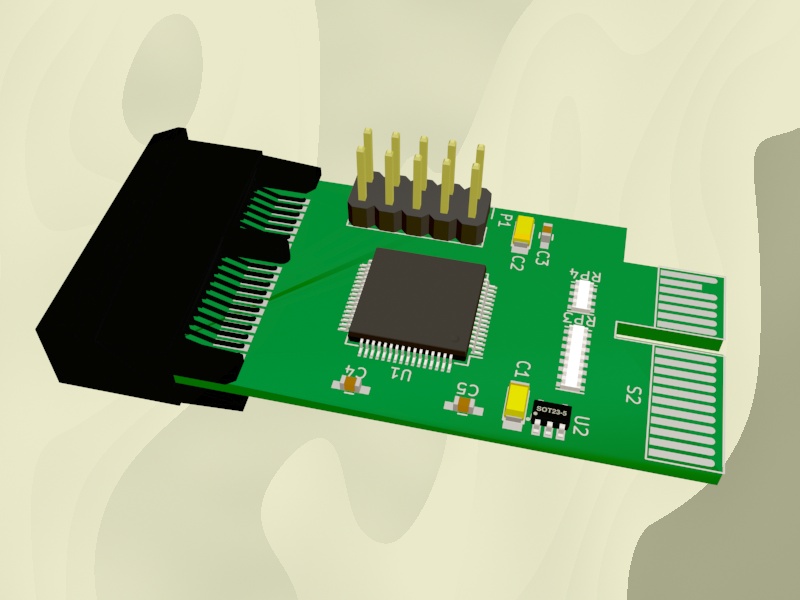

Welcome to XMOS_CPLD_SLICE board development page.

This page collects the latest informations about the development of this small board, which aimed to help the usage of xmos slice kit environment.

This extender slice board contains an ALTERA CPLD, which pre-programmed by jtag, and stores its configuration while not powered (non-volatile operation). The minimal goal to get a chaince to connect a Slice board different way, than

originally specified. Further goal is to stimulate the developer board, without need a manual interaction. All of this depends on the verilog (VHDL) code, which can be developed seperately.

This extender slice board contains an ALTERA CPLD, which pre-programmed by jtag, and stores its configuration while not powered (non-volatile operation). The minimal goal to get a chaince to connect a Slice board different way, than

originally specified. Further goal is to stimulate the developer board, without need a manual interaction. All of this depends on the verilog (VHDL) code, which can be developed seperately.

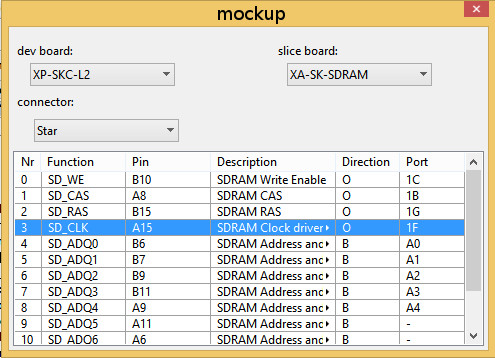

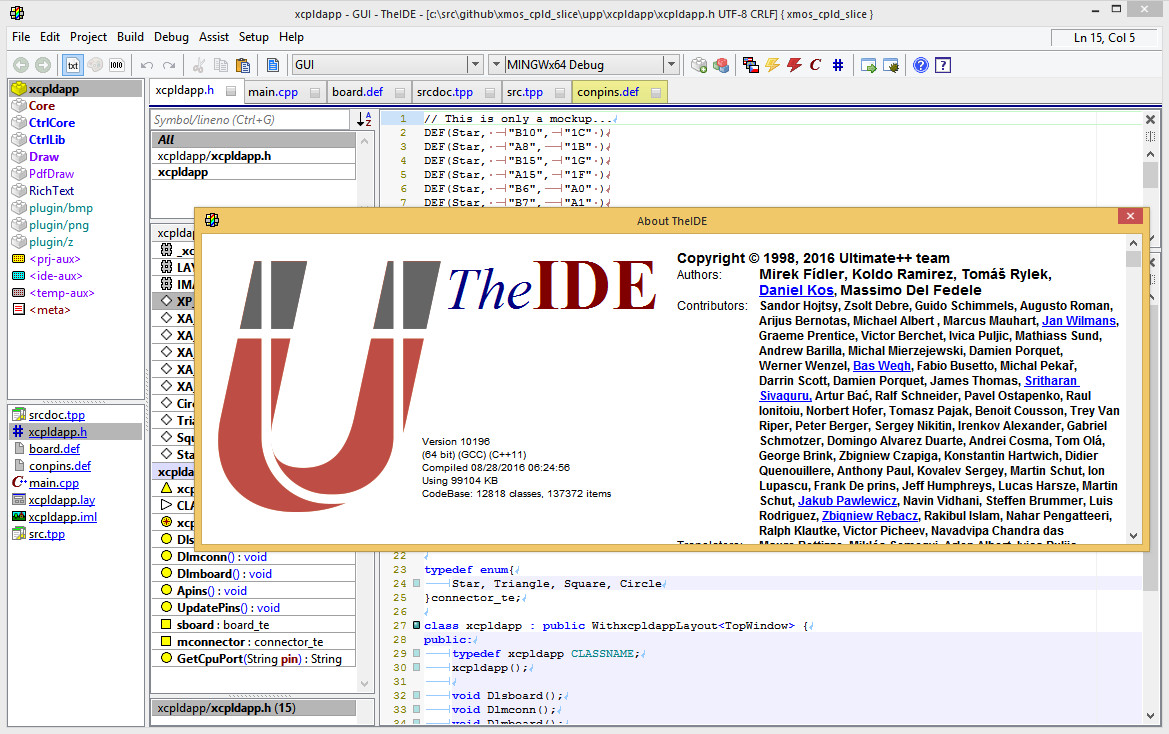

Configurator Application

We’ve created a preliminary (mockup) application yet, because of the project status is in this early phase. But you can see, the desktop application helps the configuration of the card some user-friendly way.

The plan, we generates several precompiled binaries for cpld, which contains *some* possibilities supported by the configurator too. Furthermore, developers could generate a verilog file, which compilable by ALTERA Quartus toolchain.

Creating instant testbed automaticaly

Later... The application will generate not only verilog source, but C, XC languages are further goals. On one hand, to generate and maintain the embeded code, in other hand to generate automatic stimulation codes for test bed.

Authors and Contributors

Any idea welcomed, please contact with the author: (@bfarago).

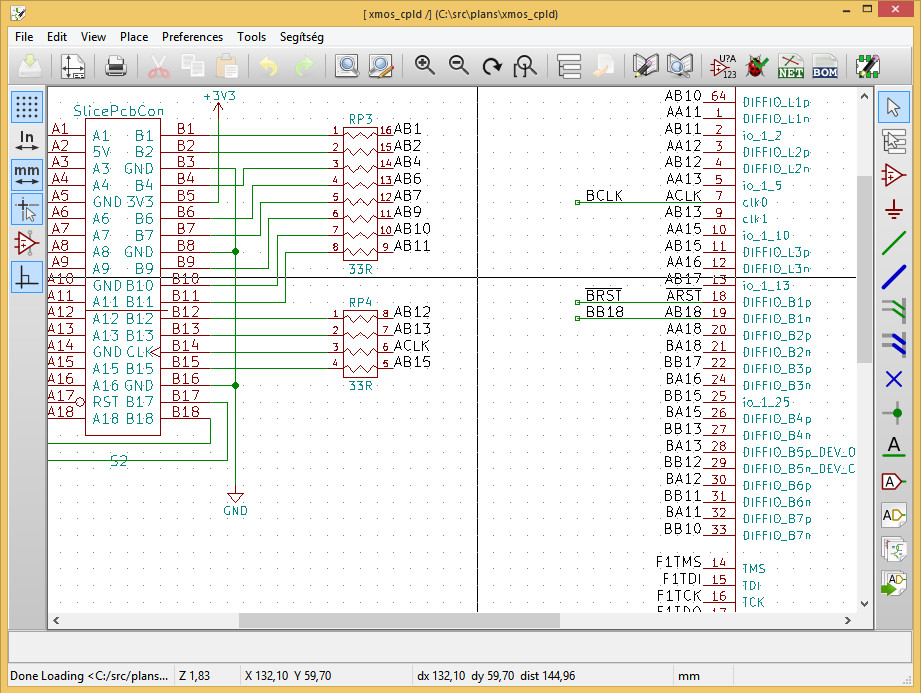

We are using KiCAD Free EDA tool for this project.

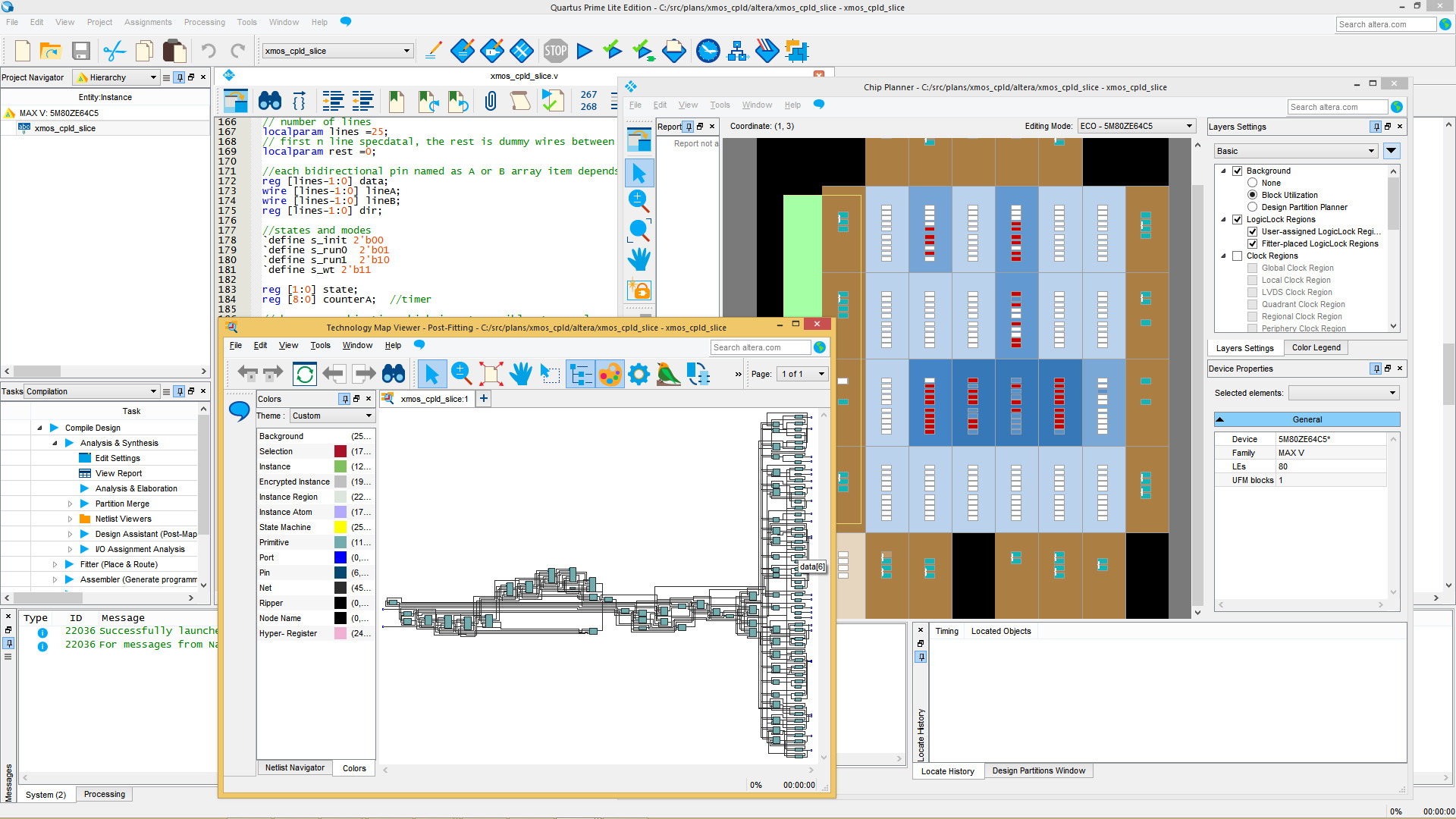

And ALTERA Quartus Prime (Free edition)to generate cpld codes.

And Ultimate++ environment for C / C++ development.

And ALTERA Quartus Prime (Free edition)to generate cpld codes.

And Ultimate++ environment for C / C++ development.

Support or Contact

For more informations, check out our documentation.